|

<이미지를 클릭하시면 크게 보실 수 있습니다> |

지난 수년 간 반도체 산업의 발전을 이끌어 온 영역은 트랜지스터였습니다. 한정된 면적에 트랜지스터 밀도를 높이는 것으로 프로세서의 연산 처리 성능을 향상시키는데 주력해왔습니다. 하지만 회로의 크기가 더 이상 작아지기 힘든 물리적 한계에 다다르면서 성능 발전의 속도 역시 더뎌졌죠. 3차원 구조인 핀펫(FinFET)에서 게이트올어라운드(GAA)로 전환하기도 했지만, 반도체 칩 발전의 불문율이었던 '무어의 법칙'을 따라가기엔 더뎌질 것이라는 관측이 잇따랐죠.

사장될 것으로 여겨졌던 무어의 법칙을 다시 한번 되살린 것이 이종접합(Heterogeneous Integration), 첨단 패키징 기술입니다. 범프·테스트 등 후방 작업에 그쳤던 후공정 영역을 첨단 공정 수준으로 높이면서 칩 성능의 발전 속도가 제 궤도에 오르게 됐죠.

이종접합 기술로 칩 성능의 발전을 이끈 대표적인 사례가 TSMC의 2.5D 패키징 솔루션 '칩온웨이퍼온서브스트레이트(CoWoS)'입니다. 칩 자체의 성능 개선을 지속하면서도, 메모리라는 다른 영역의 칩을 하나의 기판에 함께 실장하면서 또다른 가능성을 열었습니다. 이때 이종의 두개 칩을 연결하는 실리콘 인터포저는 40나노 공정 수준의 구형 공정임에도 공급 차질이 발생하는 등 높은 중요성을 드러내기도 했습니다.

2.5D IC 기술이 상용화되면서 데이터센터에 채용되기 시작했던 첨단 패키징 기술은 또다시 한 단계 도약을 준비하고 있죠. 바로 3D IC로 불리는 3D 패키징 기술을 통해서인데요. 이 기술은 현재 TSMC가 'SoIC(System on IC)'라는 기술명으로 개발 중에 있으며, 애플 역시 데이터센터·맥(Mac)용 프로세서 'M5'에 이를 적용하기 위한 절차를 밟고 있습니다. 데이터센터용 고성능 칩에 한정됐던 기술 저변이 모바일로 확대될 수 있는 계기를 마련하고 있다고 볼 수 있겠습니다.

|

<이미지를 클릭하시면 크게 보실 수 있습니다> |

2.5D 패키징은 실리콘 인터포저에 프로세서, 메모리 등 이종의 칩을 수평으로 배치해 연결하는 기술입니다. 기존 2D 패키징은 기판 위에 바로 칩을 배치하는 구조고, 와이어나 플립칩(FC)으로 연결하고, 한정된 공간 아래 개별 칩(Die)과 수동 소자를 함께 실장하기에 회로 밀도를 높이기 어렵습니다. 또 칩 간 거리가 멀어져 데이터 전송 속도가 느려지고 전력 소비가 늘어나는 단점도 있죠.

반면 2.5D 패키징은 실리콘 인터포저를 활용해 다이와 다이를 직접 전기적으로 연결하는 구조입니다. 칩 간 거리가 가까워지기에 데이터 전송 속도가 빠르고, 한정된 면적에 더욱 많은 트랜지스터를 넣을 수 있어 성능도 높아질 수 있겠죠. 특히 기존 DDR D램 대비 입·출력 단자(I/O)가 많은 고대역폭메모리(HBM)를 효과적으로 활용하고 수동 소자를 내장할 수 있다는 점에서도 이점이 큽니다.

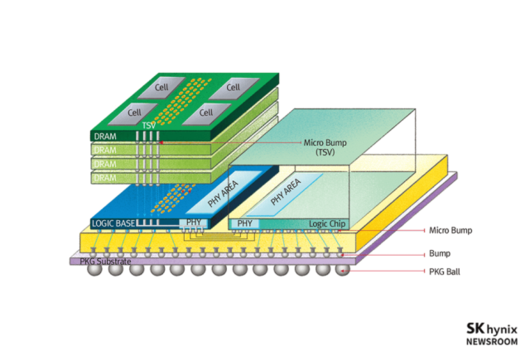

3D 패키징은 실리콘 인터포저 위에 수평으로 쌓은 칩을 수직으로 쌓은 칩입니다. 인터포저 위에 프로세서, 메모리가 일렬로 쌓인 형태로 실리콘관통전극(TSV)을 통해 메모리-프로세서-인터포저로 전극을 연결하는 구조를 띱니다. 쉽게 생각하면 HBM 내 같은 D램 간 연결을 위해 사용했던 TSV 방식을 이종 간 칩인 메모리, 프로세서에 구현했다고 볼 수 있겠습니다. 3D 패키징을 활용하면 2.5D보다도 많은 수평 면적을 활용할 수 있게 되며, 이를 제대로 활용할 수 있다면 데이터센터용 칩보다 크기가 작은 모바일 AP에도 구현하는 것이 가능해질 겁니다. 높은 AI 성능을 구현하면서도 면적을 줄일 수 있는 점 덕분에 애플이 차세대 2나노 칩을 TSMC의 SoIC로 구현하려고 하는 것이겠지요.

|

<이미지를 클릭하시면 크게 보실 수 있습니다> |

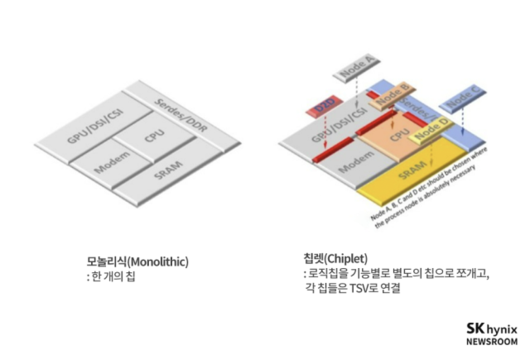

기존에는 반도체 칩의 미세회로 선폭이 그렇게 미세하지 않았기에 단일 SoC로 제작하는 것이 비용적으로 훨씬 유리했습니다. 굳이 개별 공정을 활용한 뒤 붙이는 수고스러운 작업을 할 필요가 없었던 거죠. 하지만 공정 수준이 10나노, 7나노, 4나노 등으로 접어들며 단일 SoC 제작 비용이 기하급수적으로 늘어나게 되자 칩렛이 수율·비용 측면에서 훨씬 유리한 고지를 차지하게 됐습니다.

비용·수율의 이점을 갖춘 칩렛과 많은 I/O 단자를 탑재한 3D 패키징 기술이 합쳐진다면 어떨까요. 현재보다 가격은 낮으면서도, 많은 데이터를 처리해야만 하는 AI를 구현하는데 효과적인 솔루션이 될 수 있을 겁니다. 이는 엔비디아, 애플, AMD 등 주요 팹리스가 이 기술을 채택하려는 이유죠. 혹자는 이러한 3D SoC 구성이 현실화된다면 이전에는 상상할 수 없을 만큼의 기능 구현이 가능해질 수 있다는 기대감을 품고 있기도 합니다.

이 기술에도 아직까지 난제는 있습니다. 칩렛으로 구성된 블록 간 연결을 위한 인터페이스 표준의 고도화, 정확한 전기적 연결을 위한 하이브리드 본딩 기술 등이 대표적입니다. 아울러 가격 대비 이익률이 적고, 생산성이 낮은 실리콘 인터포저를 대체하는 것도 중요한 과제로 꼽히고 있죠.

TSMC는 2.5D와 3D 패키징 기술의 비용을 낮추기 위해 실리콘 인터포저를 쓰지 않는 로컬실리콘인터커넥트(LSI) 기술을 적극적으로 개발하고 있습니다. 커다란 실리콘 인터포저를 활용하는 게 아니라 재배선(RDL) 인터포저에 내장된 브릿지 타입의 실리콘을 활용해 연결하는 방식을 주로 연구하고 있죠. TSMC는 2.5D 패키징에서 이 기술을 'CoWoS-L'이라고 명명하고 엔비디아 '블랙웰' 시리즈에 적용할 계획을 세운 바 있습니다.

삼성전자는 2.5D 패키징에서 LSI를 활용한 패키지 솔루션 '아이큐브 E(I-Cube E)'를 준비하고 있으며, 3D 패키징 솔루션 '엑스큐브(X-Cube)'도 개발하고 있습니다. 인텔파운드리서비스(IFS) 역시 2.5D 패키징 기술 '임베디드멀티다이브릿지(EMIB)', 3D 패키징 기술 '포베로스'의 기술적 고도화를 추진하고 있습니다.

- Copyright ⓒ 디지털데일리. 무단전재 및 재배포 금지 -

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.