|

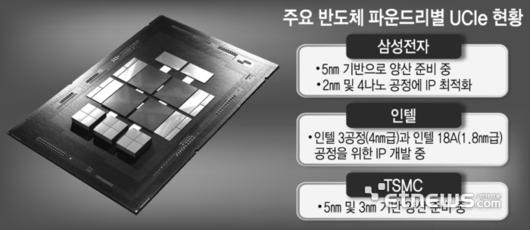

주요 반도체 파운드리별 UCle 현황 |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

초미세 반도체 위탁생산(파운드리) 공정에 '칩렛'이 침투하고 있다. 칩렛은 서로 다른 반도체를 연결해 성능을 끌어올리는 첨단 패키징 기술로, 삼성전자·인텔·TSMC 모두 3나노미터(㎚) 이하 공정에 칩렛 표준 'UCIe' 설계자산(IP) 적용을 추진 중이다. 회로 미세화 한계를 첨단 패키징 기술로 보완하려는 파운드리 업계 간 경쟁이 치열해지고 있다.

30일 업계에 따르면, 삼성전자는 2㎚와 4㎚ 파운드리 공정에 UCIe IP를 적용한 것으로 파악됐다. 최적화(커스터마이징)라고 불리는 이 작업은 삼성 2·4㎚ 고객이 UCIe를 기반으로 반도체를 설계할 수 있다는 의미다.

삼성은 올 초 5㎚ 공정에 UCIe를 최적화해 고객사 반도체 설계를 끝내고 양산을 준비 중인데, 이보다 더 미세한 공정까지 UCIe를 확대 적용하기로 했다. UCIe IP는 글로벌 반도체 IP 기업 시높시스와 협력해 만든 것으로 알려졌다.

UCIe는 업체마다 서로 다른 칩렛 기술의 호환성을 확보하려고 업계가 제정한 표준이다. 초미세 공정 전환 속도가 둔화되면서 반도체 성능을 높일 대안으로 칩렛이 급부상했는데, 마땅한 표준이 없어 삼성전자·인텔·TSMC·퀄컴·MS·구글 등이 2022년부터 개방형 표준화 작업을 시작했다. 현재 UCIe 표준 1.1까지 마련됐다.

|

UCIe |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

UCIe를 활용하면 중앙처리장치(CPU)·그래픽처리장치(GPU)·메모리 등 서로 다른 기능을 하나의 반도체 칩처럼 개발할 수 있다. 인공지능(AI) 반도체 등 고성능컴퓨팅(HPC)용 칩에 특히 필요한 기술로, 단순 설계 뿐 아니라 파운드리에 최적화해야 양산까지 성공적으로 이어질 수 있다. 업계 관계자는 “첨단 공정에, 그리고 보다 많은 공정에 UCIe IP를 최적화해야 AI 반도체처럼 고부가가치 제품을 생산할 고객을 확보할 수 있다”고 설명했다.

삼성을 비롯한 글로벌 파운드리 회사가 UCIe IP 적용에 속도를 내는 것도 이 때문이다. 인텔은 현재 18A 공정(1.8㎚급)과 인텔 3공정(4㎚급)에 적용하기 위한 UCIe IP를 개발하고 있다. 인텔은 지난해 말 업계 최초로 UCIe 상호 운용 테스트가 가능한 칩(데모)를 공개하고 향후 자사 반도체의 UCIe 표준 전환을 계획하는 등 적극적인 자세다. TSMC 역시 3㎚와 5㎚ 공정에 UCIe를 적용, 반도체 설계를 완료하고 양산을 추진하고 있다.

업계는 파운드리와 첨단 패키징 간 융합이 UCIe 경쟁력을 좌우할 것으로 내다봤다. 삼성·인텔·TSMC 등 UCIe를 다루는 파운드리는 모두 자체 첨단 패키징 기술을 확보한 상태다. 누가 더 파운드리와 첨단 패키징을 유기적으로 결합, 고객사에 앞선 칩렛 제조 서비스를 제공하느냐에 따라 시장을 주도할 수 있기 때문이다.

반도체 패키징 업계 관계자는 “반도체 설계 단계부터 첨단 패키징을 염두에 두고 개발을 시작하는 것이 최근 트렌드”라며 “이를 구현할 파운드리 역시 반도체 패키징과의 기술 결합 속도가 빨라질 것”이라고 밝혔다.

권동준 기자 djkwon@etnews.com

[Copyright © 전자신문. 무단전재-재배포금지]

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.