- UNIST 반도체 소재·부품대학원 서준기 교수팀

- 유기금속화학기상증착법 박막증착 공정법 개발

|

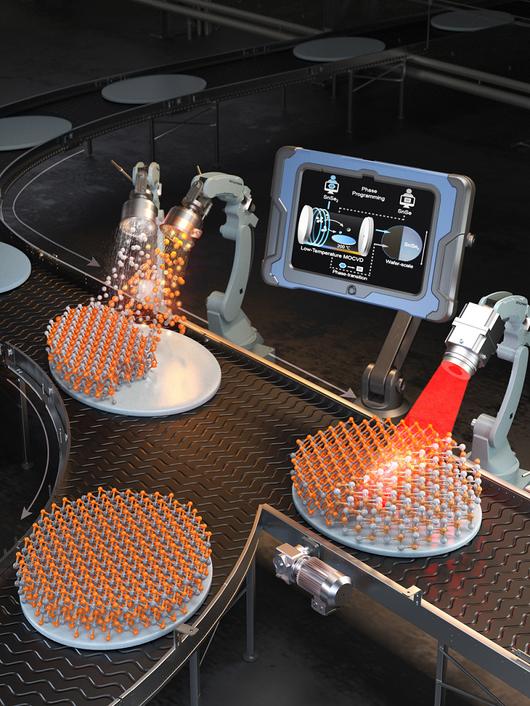

나노 분야 국제학술지 ‘어드밴스드 머티리얼즈’에 게재된 이번 연구결과 이미지.[UNIST 제공] |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

[헤럴드경제=구본혁 기자] 국내 연구진이 낮은 온도에서 원자층 두께의 막을 균일하고 안정적으로 입힐 수 있는 공정 기술을 개발했다.

울산과학기술원(UNIST) 반도체 소재·부품 대학원 및 신소재공학과 서준기 교수팀은 중국과학원 선전선진기술연구원 펑 딩 교수, 세종대학교 김성규 교수와 함께 유기금속화학기상증착법( MOCVD)을 활용해 200도의 저온에서 주석 셀라나이드계 소재별 맞춤형 공정법으로 얇은 막을 웨이퍼 단위의 대면적에 증착시킬 수 있는 박막 증착 공정법을 개발했다.

유기금속화학기살증착법은 화학반응에 참여하는 기체상의 전구체를 활용해 우수한 정밀성을 가지는 차세대 공정법이다. 반도체의 재료가 되는 웨이퍼 정도의 큰 면적에도 박막을 증착시킬 수 있다. 하지만 반응물을 합성시키기 위해선 650도 이상의 높은 온도로 리간드(수용체와 같은 큰 분자에 특이적으로 결합하는 물질)를 분해해야 했다.

연구팀은 전자소자, 광학소자, 열전소자 등 다양한 분야에서 연구 중인 2종의 주석 셀레나이드계 물질(SnSe2, SnSe)에 유기금속화학기상증착법을 적용했다. 2종의 주석 셀레나이드 박막 모두 웨이퍼 단위의 수 나노 수준 두께로 균일하게 증착시켰다.

연구팀은 낮은 온도로 증착하기 위해 리간드가 분해되는 온도 구간과 박막이 증착되는 온도 구간을 물리적으로 분리했다. 증착법에 사용되는 주석과 셀레늄 전구체의 비율을 조절하고, 전구체를 운반하는 알곤가스의 유량도 정밀히 조절했다.

이렇게 제조된 박막은 높은 결정성을 갖는다. 규칙적으로 배열되는 것이다. 증착 과정에서 물질의 상(phase)과 두께도 제어할 수 있다. 유기금속화학기상증착법을 사용했음에도 200도 정도의 저온에서 기판 종류와 상관없이 균일하게 증착됐다.

연구팀은 개발된 공정을 웨이퍼 전체에 적용했다. 2종의 박막 모두 화학적으로 변하지 않고 높은 결정성을 가졌다. 원자층 수준의 두께 조절과 균일한 증착도 가능했다. 개발된 공정법이 다양한 전자소자에 대면적으로 활용될 수 있음을 보여주는 것이다.

|

고경민(윗줄 왼쪽부터 시계방향으로) 연구원, 이욱희 연구원, 조한빈 연구원, 김성연 연구원, 서준기 교수.[UNIST 제공] |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

서준기 교수는 “이번 연구는 반도체 박막 소재 상(Phase)에 따른 고유의 열역학과 동력학적 거동 기반 공정 전략을 제시한 사례이다”며 “차세대 반도체 소재 맞춤형 공정 개발에 성공했다는 점에서 전자소자 응용 연구를 가속화 시킬 것”이라고 전했다.

이번 연구결과는 나노과학 분야 국제학술지 ‘어드밴스드 머티리얼즈’ 4월 10일 온라인 게재됐다.

nbgkoo@heraldcorp.com

Copyright ⓒ 헤럴드경제 All Rights Reserved.

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.