삼성전자, 올해 2분기 3D 패키징 출시 예고…2030년 3D D램 상용화 공식화

|

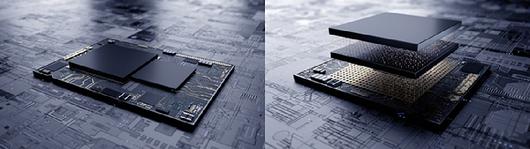

기존 시스템반도체의 평면 설계(왼쪽)와 오른쪽 삼성전자의 3차원 적층 기술 'X-Cube'를 적용한 시스템반도체의 설계 이미지. [사진=삼성전자] |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

7일 업계에 따르면 삼성전자는 2030년 3D D램을 상용화한다는 계획을 수립하고 선제적인 연구개발(R&D)을 진행 중이다. 3D D램은 데이터 저장 공간인 셀(Cell)을 평면으로 배치하던 기존 구조에서 벗어나 수직으로 쌓아 올려 단위 면적당 용량을 늘리는 기술을 적용한 반도체다.

3D D램은 기존 D램보다 작은 면적을 차지하면서도 고용량 데이터를 처리할 수 있다. 특히 고용량, 빠른 데이터 전송 속도를 비롯해 저전력 등 높은 효율성이 요구되는 AI 시대에 수요가 빠르게 증가할 것으로 전망된다.

3D D램은 최근 수요가 급증하는 고대역폭메모리(HBM)와도 차이가 있다. HBM은 D램 완제품을 여러 개 쌓은 것이지만, 3D D램은 단순히 칩을 쌓는 것이 아니라 D램 내부에서 기억 소자를 수직으로 쌓아 올리는 기술이다.

현재 D램은 기판에 최대 620억 개에 달하는 셀을 수평으로 배열한다. 촘촘하게 트랜지스터를 넣다 보니 전류 간섭 현상이 발생한다. 3D D램은 셀을 수직으로 쌓아 트랜지스터의 간격을 넓혀 간섭 현상을 줄일 수 있다. 아울러 같은 면적에 셀을 더 많이 넣을 수 있어 용량도 크게 늘어난다. 3D D램의 기본 용량은 100기가비트(Gb)로 현재 가장 용량이 큰 D램(36Gb)의 세배에 이른다.

삼성전자는 지난 3월 미국 실리콘밸리에서 열린 메모리 반도체학회 '멤콘(MEMCON) 2024'에서 내년 3D D램 초기 버전을 공개하겠다고 밝힌 바 있다. 10나노(1㎚=10억분의 1m) 이하 D램에 수직 채널 트랜지스터(VCT)를 활용하는 새로운 구조다. 여기에 제품 상용화 시점을 구체화하며 차세대 메모리 반도체에서의 선도적 위치를 공고히 하겠다는 의지를 드러내고 있다. 지난해 하반기에는 마이크론에서 3D D램 기술을 개발해 오던 이시우 부사장을 영입하기도 했다.

반도체 산업은 그동안 칩의 크기를 얼마나 줄이는지의 최첨단 미세공정 기술력이 경쟁력이었다. 파운드리(반도체 위탁생산) 업체들은 앞다퉈 1나노대 미세공정 양산을 추진 중이다. 최근 대만 TSMC는 2026년 하반기부터 1.6㎚ 공정을 통한 반도체 생산을 시작하겠다고 밝혔다. 인텔은 올해 안에 1.8㎚ 공정 양산을 선언했고, 2027년까지 1.4㎚ 초미세 공정을 도입한다는 계획이다. 삼성전자는 2025년 2나노, 2027년 1.4㎚ 공정 양산을 시작한다는 계획이다.

그러나 반도체 공정이 1나노대에 들어가면서 더 이상 미세공정을 고도화하는 것이 한계에 다다를 것이라는 게 전문가들의 전망이다. 현재 미세공정은 극자외선(EUV)으로 웨이퍼에 회로를 새겨 넣는 EUV 노광장비가 쓰인다. 네덜란드 ASML사의 EUV 노광장비가 독보적이다. 그러나 노광장비가 아무리 진화하더라도 회로 선폭이 가늘어지고 회로 간격이 좁아질수록 전기신호의 간섭이나 혼선을 피하기 어렵기 때문이다. 이 때문에 1나노대 미세공정에 들어가면 상용화할 만한 수율 확보가 쉽지 않다는 분석이다. 때문에 최근에는 회로 미세화와 함께 트랜지스터를 다양한 입체(3D) 구조로 바꿔 한계를 극복하려는 기술이 점차 각광을 받고 있는 것이다.

3D D램 개발에 앞서 서로 다른 고성능 칩을 수직으로 쌓는 '3D 패키징'은 본격적인 상용화를 앞두고 있다. 삼성전자는 지난달 30일 열린 1분기 실적발표 컨퍼런스 콜에서 "올해 2분기에 3D 패키징을 적용할 수 있는 4㎚ 파운드리 공정을 준비할 것"이라고 발표하기도 했다. 패키징은 반도체 주요 공정 중 '후공정'에 해당하는 것으로, 서로 다른 칩을 연결해 하나의 칩처럼 작동하게 한다.

3D 패키징을 통해 중앙처리장치(CPU), 애플리케이션프로세서(AP), 그래픽처리장치(GPU)와 같은 칩에 다른 공정에서 만든 칩을 쌓아 올리는 것이 가능해진다. 현재 AI 가속기에 쓰이는 HBM의 경우, GPU 옆에 HBM을 수평으로 놓는 방식의 2.5D 패키징 공법이 활용된다. 3D 키징은 칩을 옆으로 이어 붙일 필요가 없어 공간 활용도가 높아지고, 데이터 처리 속도와 전력 소모량도 줄어든다. 삼성전자와 SK하이닉스는 2026년 3D 패키징 공법으로 만든 6세대 HBM(HBM4)을 양산한다는 계획이다.

김경륜 삼성전자 반도체(DS)부문 메모리 사업부 상품기획실 상무는 최근 삼성전자 뉴스룸 기고문에서 "AI 기술 성장에는 메모리 반도체 발전이 필수적이고 시스템 고성능화를 위한 고대역폭, 저전력 메모리는 물론 새로운 인터페이스와 적층 기술도 요구되고 있다"며 "2030년 3D D램 상용화에 나설 계획"이라고 밝혔다.

/김종성 기자(stare@inews24.com)

[ⓒ 아이뉴스24 무단전재 및 재배포 금지]

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.